Official ZX Interface (ZXI™) Standard

A downloadable game

The ZXI™ (ZX Interface) standard is for devices that are attached to the Spectrum edge connector.

ZXI™ compliant devices are inter-operable with each other without conflicts. Certified devices may display the logo on their case, in their manuals, and on-screen.

Background

The Z80 provides 16-bit I/O decoding, so in theory the Spectrum has 65536 ports available for hardware devices. In practice the Spectrum does not fully decode the I/O and there are no spare I/O ports available that do not clash with at least one existing peripheral. For example, the ULA alone uses 32768 ports (every even port). It is worth noting that the Timex clones do fully decode the I/O ports.

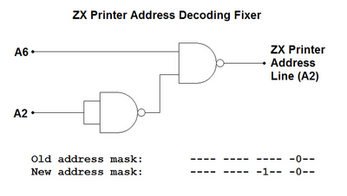

During the development of the ULAplus replacement ULA, a comprehensive search was carried out to determine a 16-bit port range that clashed with the least devices. An 8-bit port was located that clashed with a single device, the ZX Printer, and a hardware fix created to prevent the ZX Printer using that address. A modification to the ZX Printer circuit prevents it being triggered by access to port xx3B.

Meanwhile, during the development of the Spectranet ethernet card, a solution was devised to enable multiple devices to page in their own ROMs using 'ripple priority'. The ZXI standard combines these two approaches into a single standard. Legacy devices that do not use ROM paging may also be certified as ZXI compliant on a case by case basis.

Port Allocation

Port allocations are currently in flux - be advised that assignments may change in the future

To have your device certified as ZXI compliant, you must apply for the required number of I/O ports in the range #hh3B. This can be done by leaving a message in the forum.

Allocations as of 10 April 2020

It is proposed that the 256 ZXI™ ports (#xx3B) be divided into two areas based on the state of the A15 line.

A plug-in ULA replacement (such as a ULAPlus implementation) fitted in place of the original ULA can only access the A14 and A15 lines of the high address byte. This means that only partial decoding is possible and the device will respond to 128 of the available 256 ports.

A complete clone (i.e. not a plug-in ULA replacement) however can be given access to the full address bus and hence should decode the high bytes fully. It is proposed that any ports needed for internal functions in a clone (for example changing clock speed) be allocated from the higher 128 ports (i.e. A15 high).

Current ZXI™ port assignments with A15 high:

#FF : ULAplus data #FE : ZX Prism palette control #FD : ZX-UNO #FC : ZX-UNO #FB : ZXID system (draft) #EF-FB: Unassigned #EE : ZX Prism (?) #E0-ED: Unassigned #DF : Spectrastick data / ZEsarUX data #DE : ZX Prism (?) #D0-DD: Unassigned #CF : Spectrastick register select / ZEsarUX register select #CE : ZX Prism (?) #C0-CD: Unassigned #BF : ULAplus register select #BE : ZX Prism palette control #AF-BD: Unassigned #AE : ZX Prism (?) #9F-AD: Unassigned #9E : ZX Prism (?) #8F-9D: Unassigned #8E : ZX Prism (?) #80-8D: Unassigned

Current ZXI™ port assignments with A15 low:

#70-7f: MB03+ #6E-6F: SAA1099 Sound card (Implemented by MB03+ and others) #6D : SID R/W SID Control Register (MB03+) #6C : Select SID Control Register (MB03+) #40-6D: Unassigned #31-3F: Unassigned #30 : NEXT (Unofficially allocated) #26-2F: Unassigned #24-25: NEXT (Unofficially allocated) #20-23: Unassigned #16-1F: Unassigned #10-15: NEXT (Unofficially allocated) #04-0F: Unassigned #03 : Spectranet page A memory select #02 : Spectranet page B memory select #01 : Spectranet programmable trap register #00 : Spectranet control register

Port Decoding

ZXI™ compliant devices must perform complete bus decoding and take into account the M1 signal and the RFSH signal.

NMI Handling

The device must only respond to its own NMI. This is particularly important if the machine is using a ROM with a working NMI handler routine.

INT Triggering

It is possible on machines which have a straight connection from the INT signal at the rear bus, to the INT pin at the Z80 for an external devices to trigger an INT. It can block the normal ULA interrupt and inject its own INT pulses. ZXI™ compliant devices that use the INT signal should put a 0xFF on the data bus during the INTA cycle if the device does not use vector interrupts.

IORQULA/IORQGE

More detail required.

Legacy Device Certification

Legacy devices that do not use their own ROMs may also be certified as compliant on a case by case basis. For example, an AY expansion for the 48K machine that uses the same ports as the 128K machine, or an IF2 compatible Sinclair Joystick interface would both be certified compliant.

Certified Devices

- Spectranet

- SLAM+/SLAM+128 (replacement ULAs)

- divMMC (SD storage)

- MB03+ (IDE storage)

- Kempston Joystick (when fully decoded)

- Kempston Mouse (when fully decoded)

Pending Devices

- ZX-HD (does not currently implement reading ULAplus ports)

Legal

ZXI™ is a trademark of ZX Design and Media. ZXI™ is a royalty-free open standard. The official ZXI™ standard is released under the Creative Commons Attribution-Share Alike License.

| Status | Released |

| Author | ZX Design and Media |

Comments

Log in with itch.io to leave a comment.

Hi, I see no comments since 4 years, but I tried to contact for using 1 port for a new interface we're developing to emulate keyboard but require an IN/OUT port for the mode "redefine keys" so one 0xXX3B port would be a nice option. We have done initial tests using 0xF73B but maybe this ZXI standard was developed with other ports in mind for keyboard interfaces of something similar to this. Using 0xxFE or even port is not an option as the redefine keys option can be manage trough standard speccy keyboard.

Thanks in advance

Mad3001

About the interrupt triggering. Devices that are not im2 aware should not drive any value on the data bus during an intack cycle. Instead they should rely on the expansion bus pullups to ensure a 0xff value is read. Doing otherwise would be incompatible with devices that are im2 aware. The zx next will be an im2 aware computer and there are original spectrum peripherals that operated in the im2 mode, eg the amx mouse. In general, any device using standard zilog peripheral ics can be im2 enabled.

Email contact through zxdesign.info doesn't seem to have worked so I will try here.

We'd like to add an eight channel ctc to the zx spectrum next using ports 0x183B through 0x1F3B. There are no conflicts currently according to the page as it is today and I've spoken to Jan (mb03) about it already. I think he's the only other developer actively creating new hardware at the moment.

So I'll go ahead with this unless I hear otherwise.